The InGaAs IR Array of Chunghwa Telecom Laboratory

Background

In 2006, Advanced Technology Laboratory of Chunghwa Telecom proposed a collaborative project to develop homemade infrared arrays. According to the memorandum singed in the bottom half of 2006, the OIR Laboratory of IAA is in charge of measuring the performance of arrays made by AT Lab. in cryogenic temperature and evaluating the possibility of astronomical application. Our major works: interface design, controller setup, DSP programming, and gain calibration.

Array

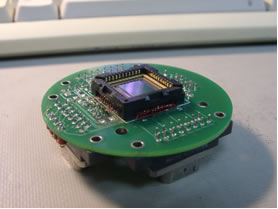

Advanced Technology Lab. developed the indium bump technology to make their InGaAs detector be adhered to the readout IC (ROIC) and form a complete array. Indigo System Corporations’ ISC9809 is adapted as the ROIC. Major specification and requirements of array:

- Resolution: 320 x 256.

- Cut off wavelength: 1.75μm.

- Pitch size: 30μm.

- CTIA input circuit with selectable integration capacitors.

- +5.5V is needed for both analog and digital operation.

- Single to 4 output parallel readout capability.

- Max. pixel rate is up to 10MHz.

- Control registers enable changing readout mode on-the-fly.

The layout of ISC9809 shown in the Figure 1 was provided by the company and the interface board, shown in the Figure 2, used to adapt array were designed by OIR, IAA.

Readout

SDSU2 system shown in the Figure 5 is used as the array controller. One clock driver board and one IR video board are installed along with a timing board. The DSP code loaded in the ROM of timing board implements following functions:

- Basic readout: following the specs shown in Figure 3.

- Control registers writing: the same technique used in WIRCam.

- CDS readout: realized by using global resetting of ISC9809 and IMRO mode. Refer to Figure 4 to get insight of the detail timing. CDS is essential for images array calibration.

Results

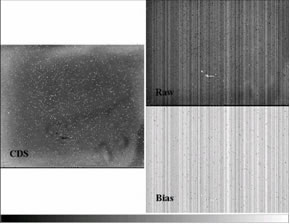

Dark imagess were taken with varied exposure time and temperature. Several points are worth to be noticed:

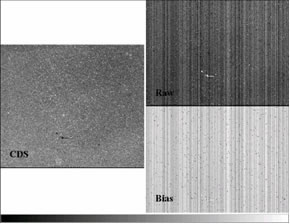

- CDS works and the vertical pattern in bias and raw imagess is removed. Refer to Figure 7 and Figure 8.

- Dark current is not improved anymore even temperature is lower than 180K. It might be the limitation of detectors.

- A weird pattern showed up while temperature is lower than 190K. After the measure of another sample, we are confident this pattern comes from the stress of filling material between the detector and the ROIC. This point has been reported to Advanced Technology Lab.

Future Work

The system gain calibration is not performed yet. Certain of modification of dewar is needed to hold the chip for a longer period. For example, the widget shown in the Figure 11 is a new tube to help LN filling process. Beyond the gain measurement, several characteristics should be measured more detailed in the next couple of runs:

- The bias fed to detector common node should be fine tuned to determine an appropriate Q point for the device. The dark level can also be verified.

- To apply different pixel rate and see how the noise varies with.

- To design a front-end amplifier on the infrared video boards with appropriate gain to accommodate the full dynamic range of the array.

- To implement multi-channel readout.

- To depict the whole picture of the array and evaluate the possibility of astronomical application.

- To evaluate the advantage and practicability of using other ROICs.

Fig.1 The pad placement of ISC9809 defines the electronic interface.

Fig.2 The array produced by AT Lab mounted on the interface board designed by OIR Lab.

Fig.3. The basic readout clock pattern that we should follow.

Fig.4 IMRO mode, to achieve the essential CDS requirement for system calibration.

Fig.5 The SDSU2 controller and the external cables.

Fig.6 The Dewar used in the project.

Fig.7 Image taken as T=180K, exposure time = 7.11sec.

Fig.8 Image taken as T=270K, exposure time = 0.84sec.

Fig.9 Mean dark of a sub-region plotted against exposure time.

Fig.10 Mean dark level of a sub-region vs. temperature of the chip.

Fig.11 The new LN2 filler to improve the filling process.